嵌入式

开发板评测

极限编程

arm开发

Aerospike

图像处理

ROS

点云

前缀和

位置式PID

IAR

资损

koa

CAPL

滤波

cisp

CSDN

信号完整性仿真

三栏布局

网上购书系统

EDA

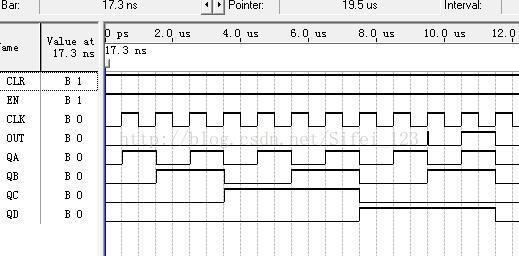

2024/4/11 20:11:23作业2:用Verilog语言实现二十进制计数器

1.新建一个工程,并且加入一个Verilog-HDL文件,参考例程中的代码编写Verilog语言,编写完成后如下图所示

编译后,查看RTL文件如下图所示 建立VWF文件,添加仿真信号后观察仿真结果如下图

调查报告——FPGA 与图像处理

数字图像处理是指将图像信号转换成数字信号并对其进行处理的过程。数字图像处理在当代社会发展中发挥着不可替代的作用,它广泛应用于几乎所有与成像有关的领域,如航空航天、生物医学工程、工业检测、机器人视觉、公安司法、军事制导、文化艺术等。随着低…

FPGA入门实验六:计数器、ROM和DDS

1.新建工程并添加Verilog和BDF文件,Bdf文件如下图: 2.RTL图如下: 3.用signal tap 对Out信号在Bus Line 模式下观察: 回答问题: 1)电路的工作频率是50Mhz,正弦波频率和计数器增量值的对应关系是什么 答&…

Skill Object处理

Skill Object处理对象处理选中对象添加对象到选择集从选择集删除对象删除对象显示对象到文件显示对象对象变换高亮对象禁止对象高亮重绘对象添加对象到cursor buffer删除对象对象处理

选中对象

axlSingleSelectObject(lo_dbid

)添加对象到选择集

axlAddSelectObject(lo_dbid…

著名EDA公司和工具介绍

一、主要的EDA软件供应商及产品 目前主流的EDA软件供应商有Synopsys、Cadence、Mentor Graphics及Magma公司。他们都有各自独立的设计流程和相应的工具,也是提供了独立的ASIC设计的整个解决方案。下表为主要的EDA产品及对应的设计流程: 这些工具各自都有…

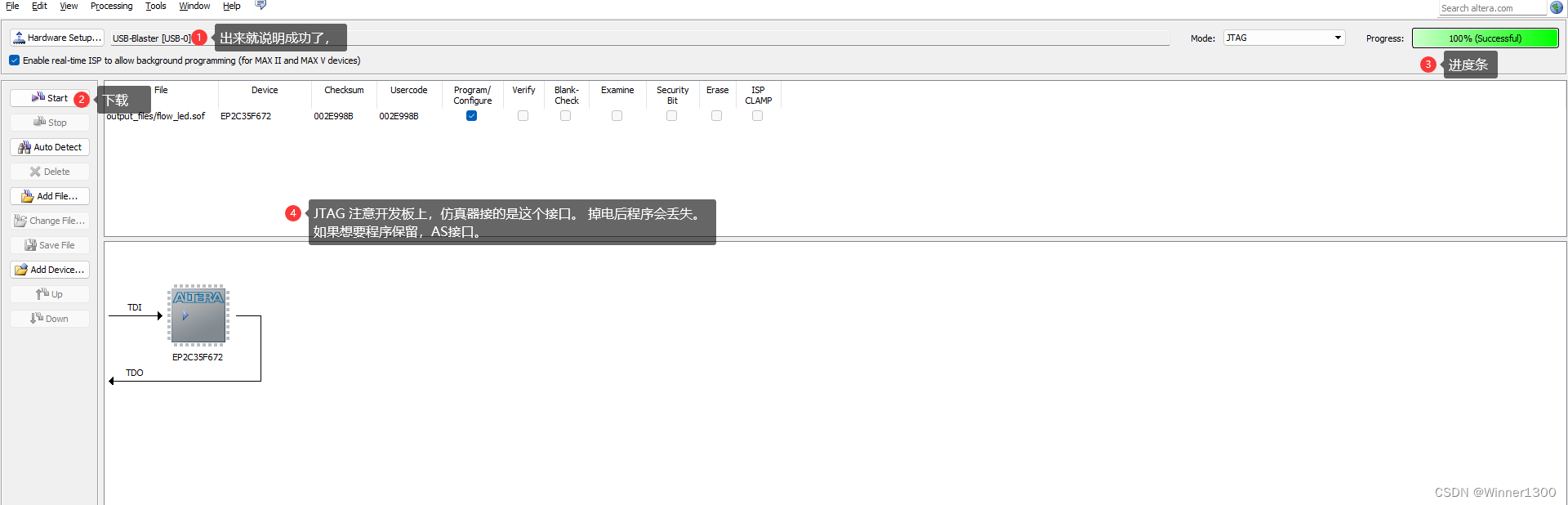

【EP2C35F672C8 EDA试验箱下载】

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档 文章目录 前言一、试验箱如何下载?1. 编译工程没问题后,配置引脚2.配置完引脚后,记得重新编译3.配置下载4.配置下载器,需要装驱…

检测序列11101000的帧头如何获取(附上源码)

教入门怎么获得你要检测序列的帧头,还是以我的上一篇文章为例。这里直接贴出源码以供大家参考学习。

本篇为获取检测序列11101000的帧头

(1)

源码

module seq_rd(input clk,input rst_n,input data_in,output [7:0] out_data0,output [7:…

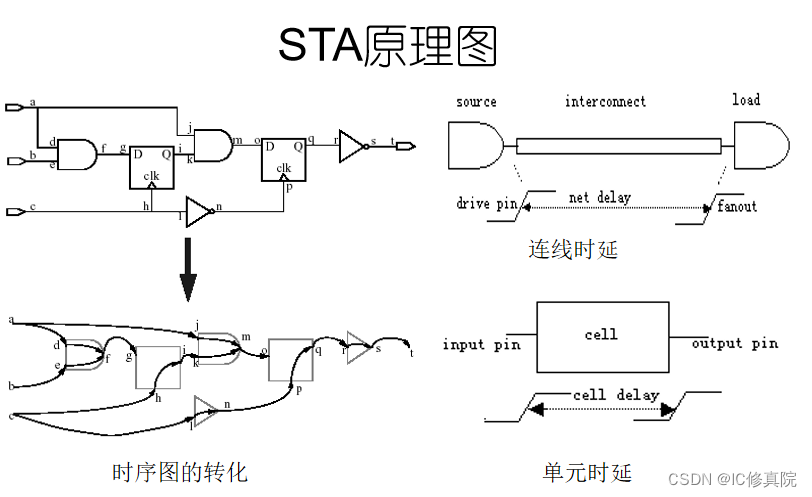

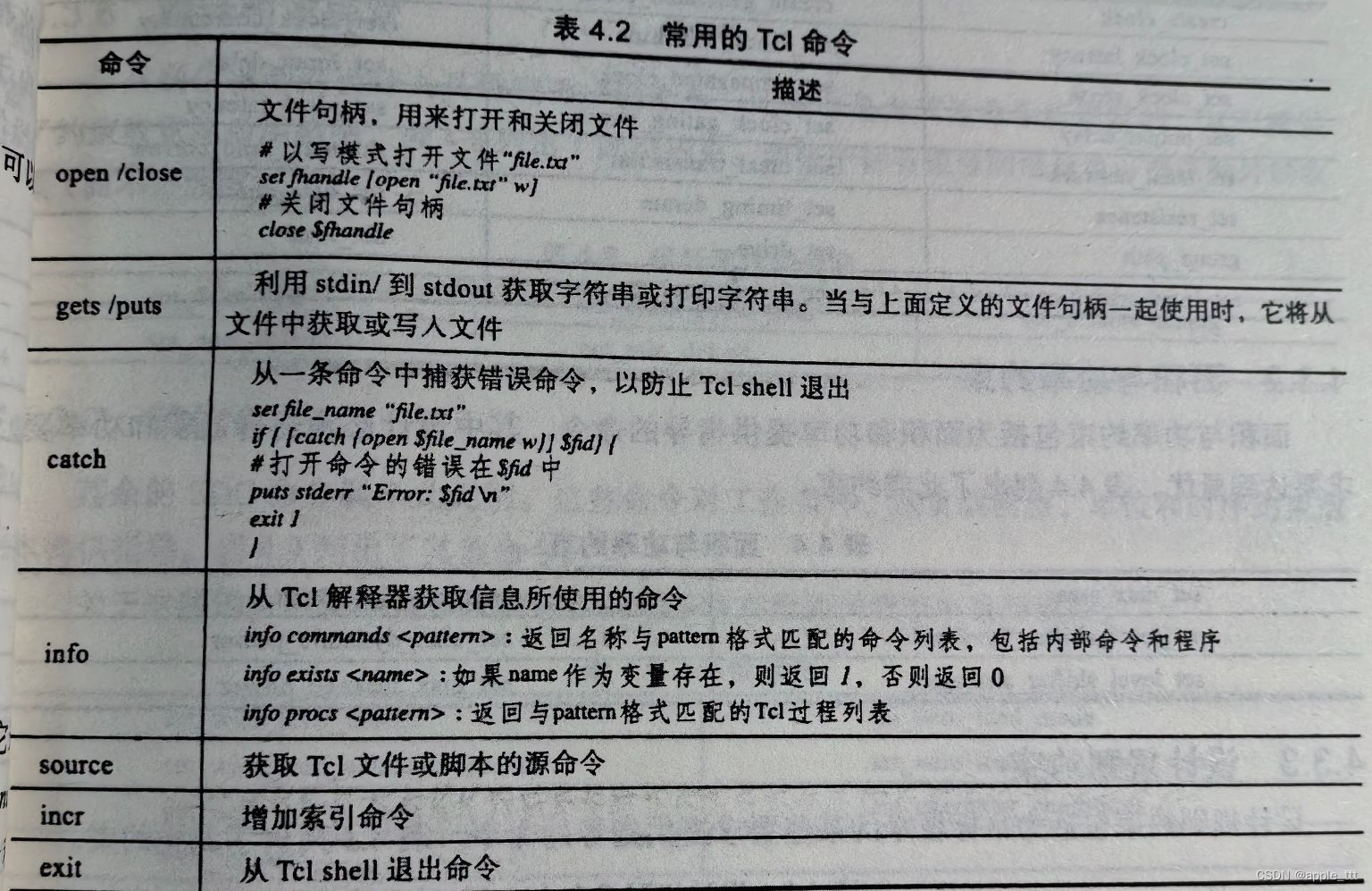

Design Compiler工具学习笔记(4)

目录

引言

知识储备

实际操作

设计源码

Vivado2018.3仿真

VCS2016仿真

Tcl脚本

约束脚本 MY_TOP.tcl

运行脚本 RUN.tcl 引言

本篇继续学习 DC的基本使用。本篇主要学习 DC 需要的环境约束。

前文链接:

Design Compiler工具学习笔记(1&#x…

kicad:应用程序在任务栏的名称如何修改?名称与预期不一致

我遇到的问题

mingw编译生成的exe,任务栏显示名称不符合预期

使用mingw编译代码时生成的eeschema.exe文件,eeschema.exe启动后在任务栏鼠标右键显示的名字并不是rc文件中的名字,为什么? 这个问题可能与 eeschema.rc 文件中的资源…

skill View File学习笔记

skill View File学习笔记判断ViewFile类型创建ViewFile判断ViewFile类型

axlIsViewFileType(g_userType

) ⇒

t/nil实例

logWindow axlUIViewFileCreate("batch_drc.log" "Batch DRC Log" t)

axlIsViewFileType(logWindow)

⇒ t创建ViewFile

axlUIView…

FPGA入门实验三:计数器、波形仿真、SignalTap

题目(1):参照代码,设计一个0-17的计数器,当计数值为17的时候,OV输出1,其他输出0,注意设定合理的信号位宽。

1.新建工程,添加BDF文件和Verilog-HDL文件,写一个…

FPGA入门实验四:时间基准电路 和 带使能的多周期计数器

题目要求:

1.根据参考代码,将计数器范围改为0~15,verilog 代码如下:

module CNT_EN( input wire CLK, input wire EN, output reg [4-1:0] OUT, output reg OV ); always (posedge CLK) begin if(EN1&&OUT<15) O…

作业2:4-16进制译码器Verilog 语句实现

1.根据工程向导新建一个工程。

2.新建VHDL-Verilog 文件,注意文件名称必须和工程名称相同。编写完成的Verilog文件如下图

3.将工程进行编译,看是否报错,无误后可以进行下一步操作。

4.查看RTL文件如下图所示 5.建立仿真VWF文件,…

作业2:循环计数器Verilog实现

1.根据工程向导新建工程

2.新建一个Verilog-HDL文件,编写相关的Verilog语句,如下图所示 3.在TOOL下的选项中查看RTL图,如下图所示。 4.建立VWF文件,添加输入信号,然后观察仿真结果如下图所示

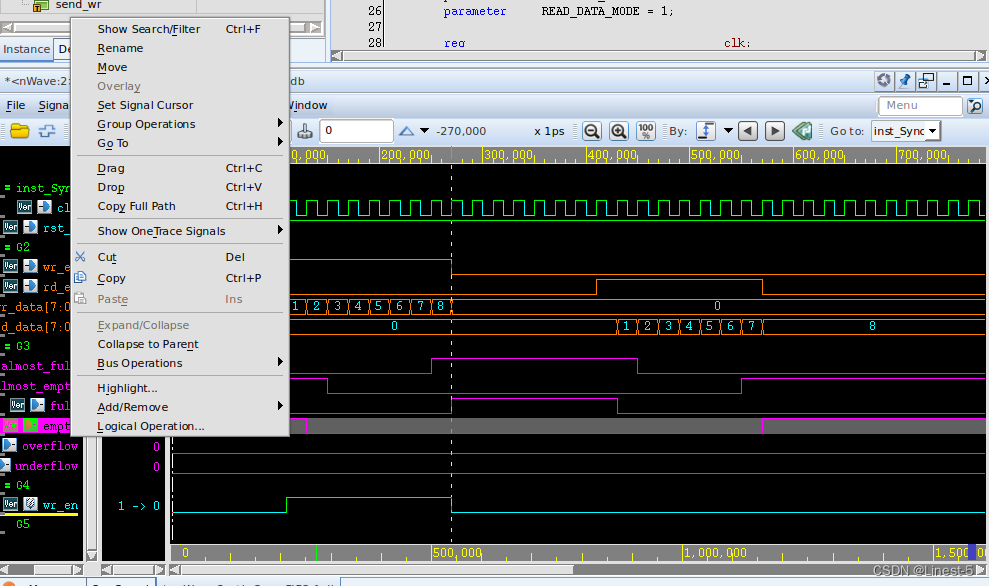

Questasim与Visualizer的livesim仿真

1.前言

Live-Simulation (live-sim)模式允许Visualizer调试环境与Questasim进行交互操作,此模式将Visualizer GUI与Questasim仿真相结合,因此可以在线调试当前仿真的结果和波形。在livesim模式中,可以在Visualizer GUI中控制仿真、设置断点(…

3D轻量引擎HOOPS SDK:EDA应用程序高效开发利器

电子设计自动化(EDA)软件在现代工程实践中扮演着至关重要的角色。随着技术的不断进步和市场的竞争加剧,开发高效、可靠的EDA应用程序成为了行业内的一项迫切需求。在这一背景下,Tech Soft 3D的HOOPS SDK(Software Deve…

【VCS Verdi】VCS Verdi 联合仿真总结

1. VCS 介绍VCS是编译型 Verilog 模拟器,它完全支持 OVI 标准的 Verilog HDL 语言、PLI 和 SDF。VCS 具有行业中较高的模拟性能,其出色的内存管理能力足以支持千万门级的 ASIC 设计,而其模拟精度也完全满足深亚微米 ASIC Sign-Off 的要求。VC…

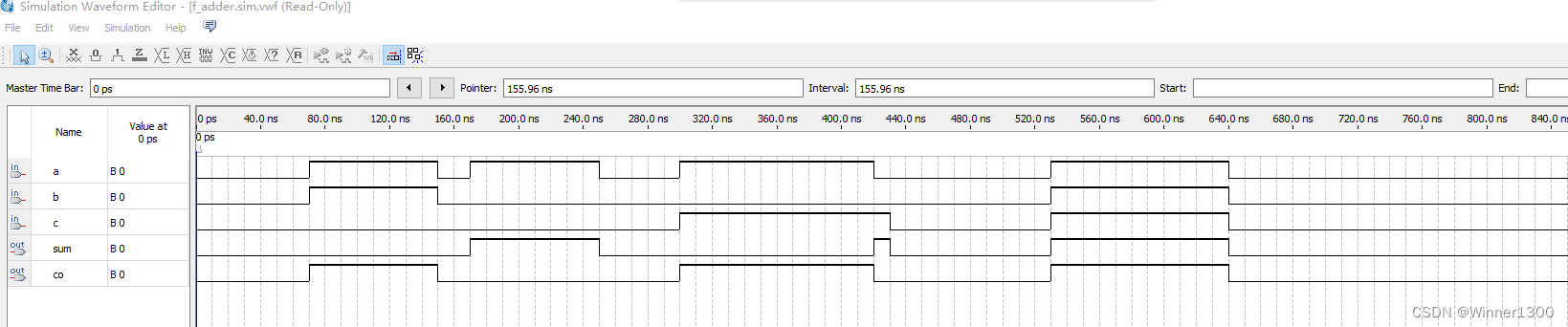

EDA 全加器设计及例化语句应用

文章目录 前言一、全加器是什么?二、使用步骤1.半加器2.全加器1.新建一个全加器工程2.添加半加器的.v文件到全加器工程中3.新建全加器.v文件,写程序,调用半加器.v文件 完成例化 三、仿真效果总结 前言

提示:这里可以添加本文要记…

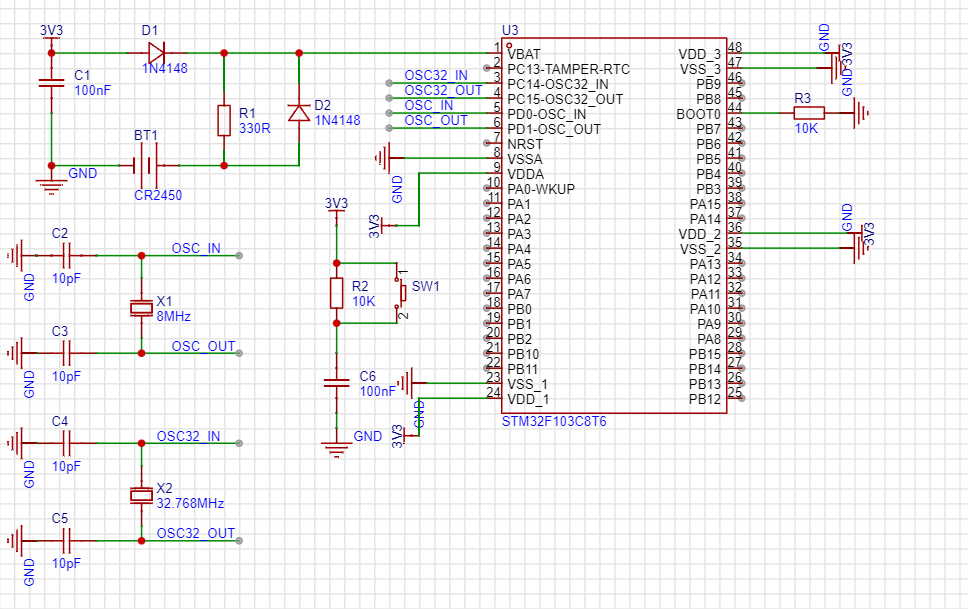

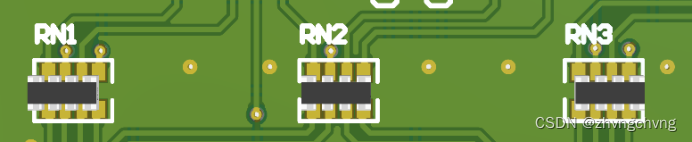

基于立创EDA的原理图设计

目录

学习目标

一、开发中原理图的作用

1.1 原理图

1.2 产品开发原理图设计阶段

1.3 原理图中的具体工作内容

二、 立创EDA软件使用基础

2.1 立创EDA电路设计软件

2.2 新建工程

2.3 设计元件原理图封装

三、项目实战(单片机最小系统) 学习目标…

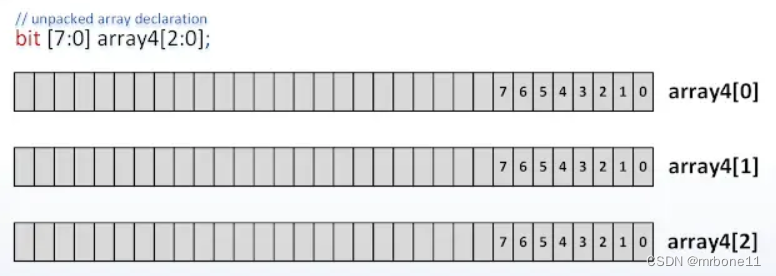

System Verilog-packed array以及unpacked array

如下声明:

logic [7:0] data [255:0]维度在标识符前面的部分称为packed array,在标识符后面的部分称为unpacked array,一维的pakced array也称为vector。

packed array

packed array只能由单bit数据类型(bit,logic,reg…

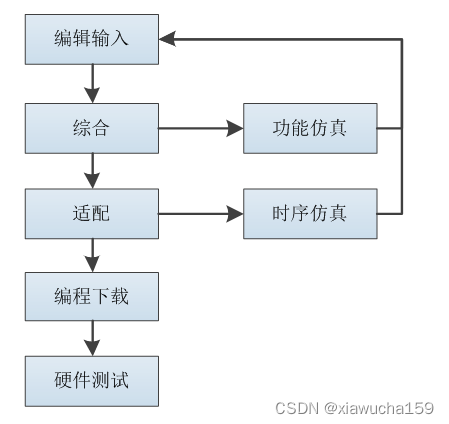

5.什么是EDA技术

目录什么是EDA技术?概念分析EDA的设计流程什么是EDA技术?

概念

EDA(ELEctrinic design automation)是指以计算机为工作平台,融合了应用电子技术、计算机技术、信息处理和智能化技术等,进行电子产品自动化设计的一门新技术。 使用…

数字IC设计流程是怎么样的,有那些eda工具? (全流程详解)

我们通常会将数字IC的设计过程分为两个部分,分别为:前端设计和后端设计。

前端设计的主要流程:

1、规格制定 芯片规格: 芯片需要达到的具体功能和性能方面的要求

2、详细设计 就是根据规格要求,实施具体架构,划分模…

LSF live reconfiguration

背景

LSF的配置管理相对比较原始,通过配置文件设置集群中的各种参数。管理员在修改LSF参数时需要很多的手工操作:先通过编辑器修改配置文件,然后还要运行一个或两个命令才能激活配置,而且配置也不是立即生效,还有几秒…

在centos7下面编译kicad

1、C17 参考链接: https://blog.csdn.net/mandiheyanyu/article/details/118995670

2、git 安装步骤:

yum install curl-devel expat-devel gettext-devel openssl-devel zlib-devel perl-ExtUtils-MakeMaker yum remove git make prefix/usr/local/gi…

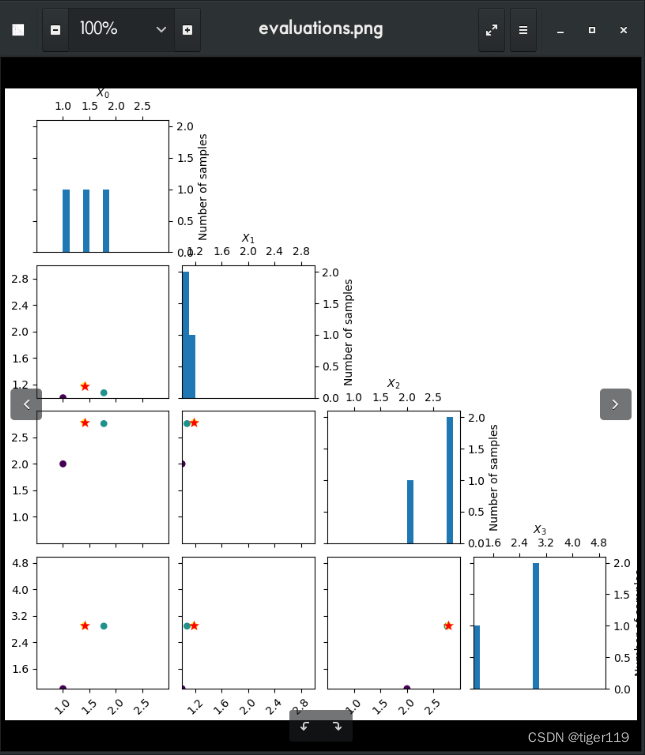

EDA工具开发中的调参方法

一:问题提出

在开发EDA工具时,涉及到复杂算法的每个Flow,有很多的参数需要设定默认值。默认值和算法有关,不同默认值效果大不相同。并且,对于不同目标,默认值的设置也不相同。如果参数很多,很难…

sweetviz工具避坑和简单使用

网上关于sweetviz的文章比较少,有些坑这里说一下给大家避坑。

使用sweetviz遇到的错误如下:

KeyError: “None of [‘index’] are in the columns”AttributeError: ‘DataFrame’ object has no attribute ‘iteritems’ ( iteritems在pa…

安装SCL后仍然提示lmgrd: Command not found.的解决办法

安装好SCL,设置好环境变量path但是仍然报错,lmhostid也是同样的错误。结果在万能的EETOP的某层回复里找到解决办法:安装OS对应的lsb包。 本人系统CentoOS 64bit, 所以切换到root账号:

yum install redhat-lsb.x86_64

问题解决

【EDA Tools】Spyglass 检查 Verilog 和 SystemVerilog 混合语言及 Lint 检查

目录 写在前面

读入设计

发现问题并解决

Lint 检查 写在前面

Spyglass可以用于检查混合设计中的语言互操作性和一致性问题。对于设计中包含多种硬件描述语言的情况,Spyglass 能够识别并解析其中的模块及其互连,并对其进行验证。例如,在包含 Verilog 和 VHDL 的混合设计中…

docker 使用 vcs/2018 Verdi等 eda 软件

好不容易在ubuntu 安装好了eda软件,转眼就发现了自己的无知。

有博主几年前就搞定了docker上的EDA工具。而且更全,更简单。只恨自己太无知啊。

Synopsys EDA Tools docker image - EDA资源使用讨论 - EETOP 创芯网论坛 (原名:电子顶级开发网…

Intel FPGA 技术开放日

概要

时间:2023.11.14 全天 ( 9:00 - 16: 20)

地点:北京望京. 凯悦酒店

主题内容:分享交流了Intel FPGA 产品技术优势和落地实践方案。

会议的议程 开场致词: FPGA业务,是几年前intel收购而…

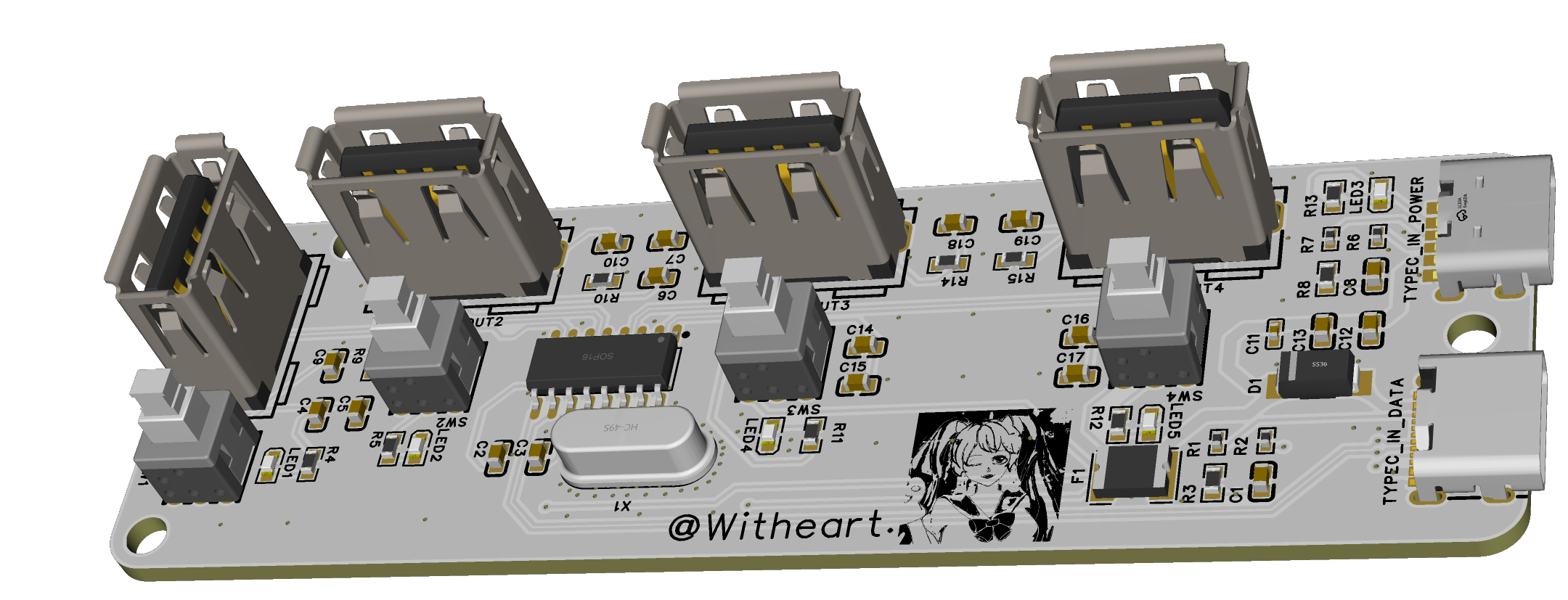

【项目实战】【已开源】USB2.0 HUB 集线器的制作教程(详细步骤以及电路图解释)

写在前面

本文是一篇关于 USB2.0 HUB 集线器的制作教程,包括详细的步骤以及电路图解释。 本文记录了笔者制作 USB2.0 HUB 集线器的心路历程,希望对你有帮助。 本文以笔记形式呈现,通过搜集互联网多方资料写成,非盈利性质…

74161设计二十进制计数器

1. 2^4<20<2^8,因此在设计中要用到两片74161芯片。

2. 新建BDF文件,保存工程。

3.将所需要的元器件和引脚拖入区域内并完成连接,如图1所示 图1. 二十进制计数器连接图

4.建立VWF文件,仿真后得到结果如图2 图2、 仿真结…

作业2:用Verilog实现12进制计数器

1.新建工程文件

2.新建Verilog文件,注意文件名称必须与工程相同, 编写完成后的文件如下图所示

通过TOOL工具栏的相关选项查看工程的RTL文件如下图所示 通过建立VWF仿真文件,并且加入使能信号、时钟信号后观察仿真的结果如下图所示。

用74161设计十二进制计数器

1.74161为十六进制计数器,设计十二进制计数器时1片就可以满足要求。

2.新建BDF文件及保存工程同前篇。

3.将所需要的元器件和引脚拖入区域内并完成连接,如图1所示 图1 十二进制计数器连接图

4.建立VWF文件,仿真后得到结果如图2

FPGA入门实验五:多周期移位寄存器

题目要求 1.根据题目要求新建Verilog创建对应的module并生成 symbol,代码如下 移位寄存器 / module shift_reg_SIPO( RST , // 异步复位, 高有效 CLK , // 时钟,上升沿有效 EN , // 输入数据串行移位使能 IN , // 输入串行数…

FPGA入门实验二:译码器组合逻辑

题目(1):放置2个2-4译码器模块,则总共有2组SW,每组2个,2组LED,每组4个,每组SW分别控制其对应的LED组

1.新建VHDL-Verilog文件,并写一个2-4译码器的moudle,并…

skill快捷键设置

skill快捷键设置创建快捷键获取快捷键查询快捷键保护快捷键创建快捷键

axlSetAlias(t_aliasg_value

) ⇒

t/nil实例

axlCmdRegister( "sgAliasDemo" sgAliasDemo

)defun(sgAliasDemo ()println( "this is a alias demo" )

)

axlSetAlias("CZ"&…

allegro skill表单学习笔记

allegro skill表单学习笔记表单表单操作流程表单格式表单选项Button定义POPUP定义Message定义TILE定义TABSET定义TAB定义文本定义GROUP定义FIELD定义FIELD操作函数LIST定义BUTTON定义CHECKLISTGRID定义表单

表单操作流程

打开表单:axlFormCreate初始化Field&#…

skill shape操作笔记

skill shape操作笔记创建shape创建简单shape(没有void)创建带Void的shapeShape APIaxlDBCreateOpenShape闭合"open"状态shape获取open"状态的shape创建圆形void创建任意多边形void创建close的shapeaxlDBCreateRectangleaxlShapeAutoVoid改变shape类型删除shape的…

FPGA入门实验一: 项目创建、编译和下载

1.选择New Project Wizard 新建一个工程,工程名称和顶层文件名称相同,如下图

2.选择芯片型号 Cyclone III 下484个引脚的EP3C16F484C,然后直接点击Finish完成创建即可。 3.为工程添加.BDF文件,取名和工程文件相同 4.在BDF文件的空…

docker 里使用vcs 2018 verdi等eda 图形界面

书接上文。之前借用别人的docker,使用EDA工具,苦于没有图形界面。如果只是编码,编译可能问题不大,但是如果要看波形之类的,就没法实现了。

docker 使用 vcs/2018 Verdi等 eda 软件-CSDN博客https://blog.csdn.net/guy…

如何将立创EDA中的元器件封装快速导入到AD软件中去

在使用AD软件画PCB的时候,最费时间的就是找元器件的封装。有的元器件如果库里面没有封装的话还得自己手动画,这样会浪费很多时间。 由于立创EDA里面的元器件比较全,而且好多器件都带有封装。那么就可以直接将立创EDA中元器件的封装直接导入到…

LSF 主机状态 unavilable 分析

在LSF集群运行过程中,有时主机状态会变为 unavilable,此状态表明主机上的 LIM 服务中断。

影响分析

那么主机上的 LIM 服务中断的影响是什么呢?

我们需要先明白 LIM 服务的功能是什么。主机上 LIM 服务的功能主要是收集主机上的资源信息&a…

2. 分享三篇早期的FPGA 布局布线论文

1. PathFinder:一种基于协商和性能驱动的FPGA布线器

Larry MCMURCHIE, Carl EBELING. PathFinder: A Negotiation-Based Performance-Driven Router for FPGAs, February 1996[J/OL]. February 1996

针对FPGA布线中存在的布线性能与可布通性之间的矛盾,该文提出了…

【PCB设计】嘉立创EDA器件3D模型导入AD的方法

嘉立创EDA器件3D模型导入AD的方法 一、嘉立创EDA导出3D模型二、CAD编辑3D模型三、AD中加载3D模型 一、嘉立创EDA导出3D模型

在嘉立创EDA中找到对应的元器件,并生成PCB,选择导出3D文件

导出元件step模型

二、CAD编辑3D模型

用FreeCAD打开模型

删除…

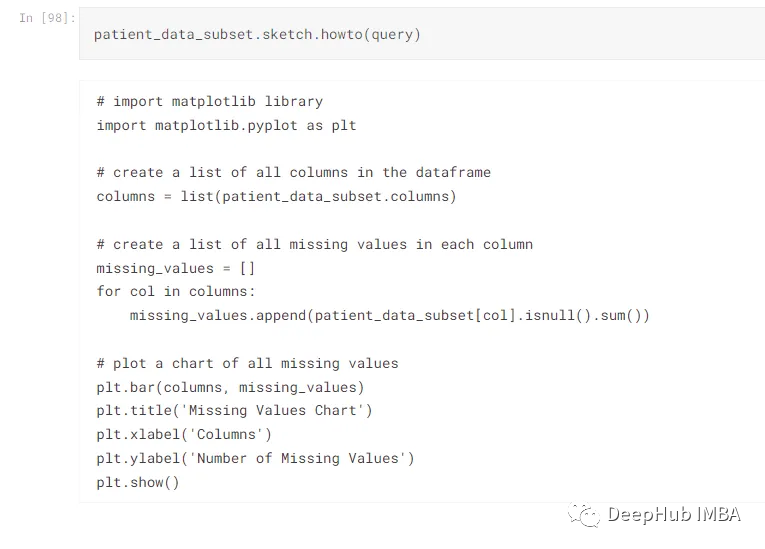

2023年5个自动化EDA库推荐

EDA或探索性数据分析是一项耗时的工作,但是由于EDA是不可避免的,所以Python出现了很多自动化库来减少执行分析所需的时间。EDA的主要目标不是制作花哨的图形或创建彩色的图形,而是获得对数据集的理解,并获得对变量之间的分布和相关…

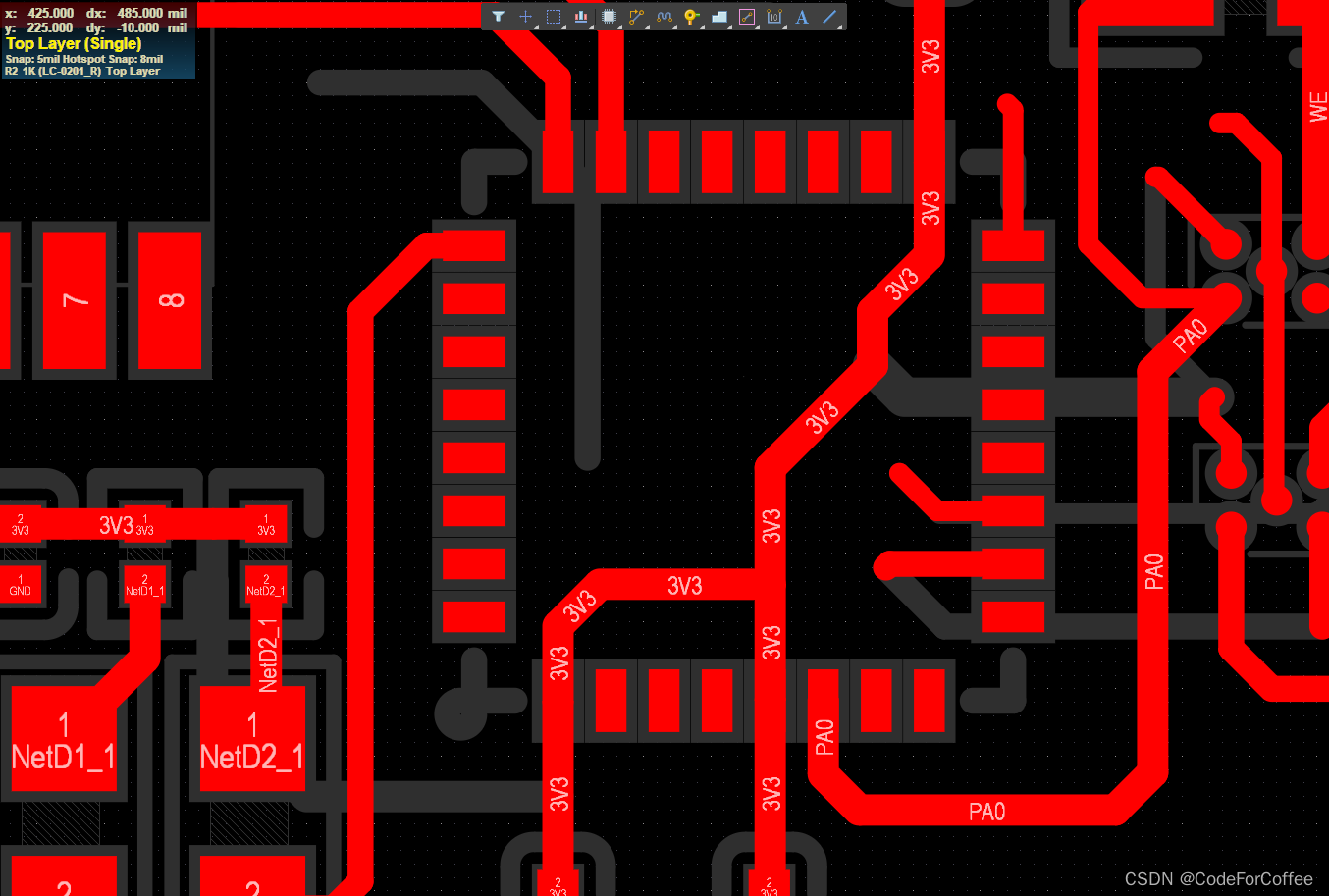

Altium显示/隐藏白色网络

在Altium软件中,相同网络的单元如果没有连接,会在PCB中出现白色的线,如下图所示。 这些白色的细线用于提示我们还有哪些网络没有布线。

如果我们不想要出现这种线,可以进行如下设置

View > Connections > Hide All 如…